|

Ремонт DVD плееров практическое руководство, советы и схемы |

|

Ремонт DVD плееров практическое руководство, советы и схемы - бесплатный интернет проект созданный с целью обучить навыкам ремонта DVD-плееров, выявить типовые неисправности и ошибки.

Ресурс будет полезен широкому кругу людей: профессионалов и радиолюбителей.

DVD-ПРОИГРЫВАТЕЛИ PHILIPS

Модель: DVDQ50

Общие сведения и технические характеристики

DVD-проигрыватель DVDQ50 фирмы Philips предназначен для воспроизведения видео — и аудиозаписей с DVD (DVD Video, DVD+RW) и CD (Video CD, SVCD, CD-R CD-RW).

Время воспроизведения однослойного DVD составляет 2 часа 15 минут, двухслойного DVD — 4 часа, двухстороннего однослойного DVD — 4 часа 30 минут, двухстороннего двухслойного DVD — 8 часов, CD — 74 минуты (для CD диаметром 12 см) и 20 минут (для CD диаметром 8 см).

Проигрыватель питается от сети переменного тока 50/60 Гц напряжением 110 ... 240 В.

Он имеет массу приблизительно 3 кг и линейные размеры: 435 мм х 72,5 мм х 291 мм.

Горизонтальное разрешение составляет 720 (DVD) и 352 точки (VCD), а вертикальное разрешение — 576 (DVD) и 288 (VCD). Сигнал изображения, кроме обычного, так называемого композитного выхода — выхода ПЦТС (SVBS), может выводиться через выходы S-Video и компонентные выходы Y, Pb/Cb, Рг/Cr. Аудиосигналы могут выводиться в аналоговой форме как моно и стереосигналы, а также в формате 5+1. В цифровой форме аудиосигналы могут выводиться через коаксиальный разъем или разъем OPTICAL в форматах IEC958 для CDDA / LPCM и IEC1937 для MPEG1/2, Dolby Digital или DTS.

Проигрыватель DVDQ50 может быть укомплектован разными выходными разъемами, в зависимости от региона предназначения. Так для большей части мира в качестве выходных разъемов устанавливаются разъемы RCA и 4-хконтак-тный разъем MiniDIN (для выходов S-Video), а для Евросоюза и ряда других стран — разъем SCART.

Основные параметры выходных аналоговых видеосигналов приведены в табл. 5.1, а аудиосигналов — в табл. 5.2.

Таблица 5.1

Основные параметры выходных видеосигналов

| Выходы | Сигналы | Параметры |

| Композитный видеовыход (CVBS | ПЦТС | Размах 1 В на нагрузке 75 0м |

| Выход S-Video | Сигнал яркости | |

| Сигнал цветности | Размах 0,3 В на нагрузке 75 0м | |

| Компонентный видеовыход (Y, Pr/Cr, Pb/Cb) | Y — сигнал яркости | Размах 1 В на нагрузке 75 0м |

|

Рг/Сг—

цветоразностный сигнал красного |

Размах 0,7 В на нагрузке 75 Ом | | |

|

Pb/Cb—

цветоразностный сигнал синего |

Основные параметры выходных аналоговых аудиосигналов

| Параметры | ^попаши ОПСПСТ1НЯ | |||

|

Диапазон

воспроизводимых частот |

DVD | Частота выборки, кГц | 48 | 4 Гц .. 22 кГц |

| 96 | 4 Гц... 44 кГц | | |||

| Video СО | 44,1 | 4 Гц... 20 кГц ! | ||

| СО | 44,1 | 4 Гц .20 кГц j | |||

| Отношение сигнал/шум на частоте 1 кГц | ИОдБ | |||

| Динамический диапазон на частоте 1 кГц | 100 дБ | |||

| Коэффициент перекрестных искажений на частоте 1 кГц | 110 дБ | |||

| Коэффициент нелинейных искажений (суммарное значение) | 98 дБ |

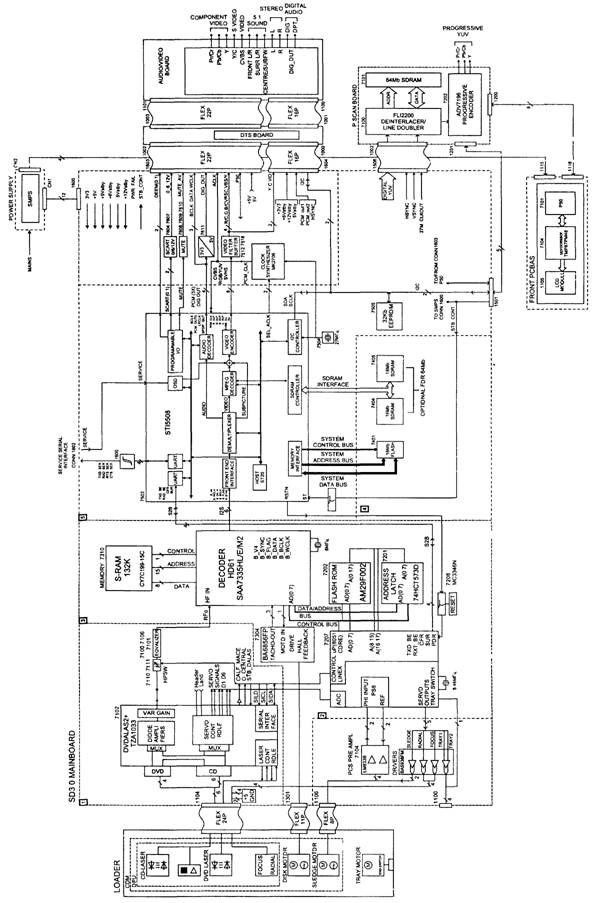

Функциональная схема DVD-проигрывателя DVDQ50 фирмы Philips представлена на рис. 5.1, а схема соединений — на рис. 5.2.

DVD-проигрыватель DVDQ50 содержит следующие конструктивные узлы:

— SD3.X LOADER ASSY;

— [1001]* A/V BOARD;

— [1002A] FRONT A;

— [1002B] FRONTB;

— [1003]DTSBD;

— [1005] POWER SUPPLY BOARD;

— [1006] SINGLE SCART BOARD (только для европейской версии);

— [1007] P.SCAN BOARD.

*B квадратных скобках указан позиционный номер узла в соответствии с рис. 5.2 и другой фирменной документацией.

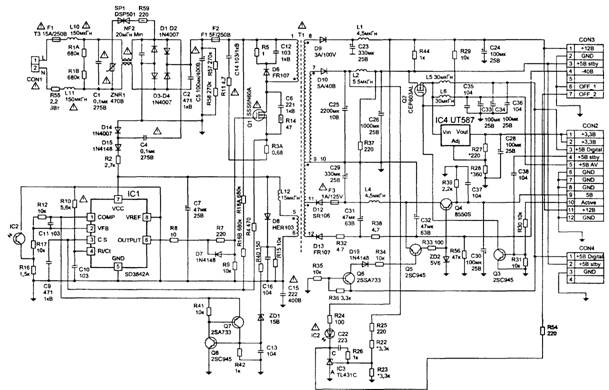

Импульсный блок питания

В модель DVDQ50 могут устанавливаться две модификации импульсного блока питания ([1005] POWER SUPPLY BOARD). Для стран ЕС это блок имеет наименование ЕРМ (Part № 3122 427 22920 или 22930), а для остальных стран — Billion (Part № 3139 248 70851). В странах СНГ можно встретить комплектацию проигрывателя как с одним, так и с другим блоком.

Импульсные блоки питания Billion и ЕРМ, как и DVD-проигрыватель, имеют два режима работы: рабочий (operational) и дежурный (standby). ИБП обеспечивают узлы DVD-проигрывателя соответствующими напряжениями питания в каждом из этих режимов (см. табл. 5.3). При этом обеспечивается групповая, а по некоторым каналам еще и раздельная стабилизация напряжений. Оба ИБП обеспечивают гальваническую развязку остальных узлов DVD-проигрывателя от питающей сети.

Таблица 5.3

Выходные напряжения ИБП проигрывателя DVDQ50

| Обозначение на принципиальной схеме | Значение,В | Примечание |

| +12V_stdby | 12 |

Используются

в дежурном и рабочем режимах |

| +5V. stdby | 5 | |

| +5V_digital | 5 | |

| i +5VAV | 5 | Используются только в рабочем режиме |

| 3V3 | 3,3 | |

| -5V | -5 | |

|

1

1 -40V |

-40 |

Микросхема SD3842A — это аналог более распространенной микросхемы UC3842A. Она представляет собой ШИМ контроллер для импу—

льсных источников питания, управляющий внешним ключом на полевом транзисторе со структурой МДП. Эти микросхемы могут изготавливаться в разных типах корпусов. В блоке питания Billion используется микросхема в корпусе DIP-8. Функциональная схема этой микросхемы представлена рис. 5.3, а назначение выводов — в табл. 5.4.

Таблица 5.4

Назначение выводов микросхемы ШИМ контроллера SD3842A (UC3842A) в корпусе DIP-8

| Выводы | Обозначение | Назначение |

| 1 | C0MP | Выход усилителя ошибки для подключения I цепи корректирующей 00С (Compensation) |

| 2 | VFB | Инвертирующий вход усилителя ошибки, на который поступает управляющее напряжение 00С (Voltage Feedback), обеспечивающее стабилизацию выходных напряжений источника питания |

| 3 | CS | Вход сигнала от датчика тока (Current Sense) выходного ключа |

| 4 | Rt/Ct | Вывод подключения времязадающей цепи Определяет максимальное значение рабочей частоты преобразователя (до 500 кГц) |

| 5 | GND | Общий , |

| 6 | Output | Выход импульсов управления выходным полевым ключом |

| 7 | VCC | Вход напряжения питания |

| 8 | VREF | Выход стабильного напряжения 5 В для питания времязадающей цепи |

Микросхема SD3842A имеет следующие особенности:

• максимальное значение рабочей частоты преобразователя — до 500 кГц;

• питание времязадающей цепи стабильным напряжением 5 В от внутреннего стабилизатора микросхемы через выв. 8;

• в цепях питания микросхемы используется пороговое устройство с гистерезисом UVLO (Undervoltage Lockout), которое при включении подает напряжение питания VCC с выв. 7 на внутренний стабилизатор (когда его значение достигнет 16 В) и отключает его при уменьшении напряжения на выв. 7 до 10 В (эту схему еще называют «старт-стопной»);

• микросхема имеет защиту от перегрузки по току выходного ключа. Для этого последовательно в цепь истока МДП транзистора (силового ключа) устанавливается резистор — датчик тока. Пилообразное напряжение обратной связи пропорциональное току выходного ключа с датчика тока поступает на выв. 3 микросхемы;

Рис. 5.f. Функциональная схема DVD-проигрывателя DVDQ50

Puc. 5.3. Функциональная схема микросхемы ШИМ контроллера SD3842A (UC3842A)

• микросхема имеет тотемный выход (двухтактный каскад на комплементарных биполярных транзисторах).

Рассмотрим работу ИБП Billion по принципиальной схеме, которая приведена на рис. 5.4.

Назначение основных элементов ИБП Billion приведено в табл. 5.5.

Сетевой выпрямитель ИБП собран на диодах D1... D4. На его входе установлен помехоподав-ляющий фильтр, а на выходе — фильтрующий конденсатор С5. Все указанные цепи достаточно просты и дополнительных пояснений не требует.

Варистор ZNR1 и искровой разрядник SP1 защищают ИБП и весь аппарат от перегрузки при значительном увеличении напряжения сети. Например, при грозовом разряде (молнии). Резистор R55 ограничивает ток заряда конденсатора С5, защищая тем самым диоды выпрямительного моста от перегрузки в момент включения аппарата в сеть.

Постоянное напряжение 290...310 В (для сети -220 В), полученное на выходе сетевого выпрямителя, обеспечивают питание импульсного преобразователя.

Рис. 5.4. Принципиальная схема ИБП Billion

Таблица 5.5

Назначение и типы (номиналы) основных узлов ИБП Billion

| Позиционные номера | Типы или номиналы | Назначение | ||

| 1 Первичные цепи | ||||

| D1...D4 | 1N4007 | Сетевой выпрямительный мост | ||

| SP1 | DSP501 | Искровой разрядник цепи защиты ИБП при увеличении напряжения сети | ||

| IC1 | SD3842A(UC3842A) | ШИМ контроллер | ||

| R12 | 10 кОм | Резистор ООС, задает коэффициент усиления напряжения усилителя ошибки | ||

| С11 | 0,01 мкФ | Конденсатор коррекции (ООС по высокой частоте), обеспечивает устойчивую работу усилителя ошибки на ВЧ |

|

|

| Q1 | SSS6N60A | Выходной ключ импульсного преобразователя ИБП на полевом транзисторе с N-каналом | ||

| R3A | 0,68 Ом 1 Вт | Датчик тока транзистора Q1 | ||

| С12 | 0,01 мкФ 1 кВ | Демпфирующая цепь |

|

|

| R5 | 1 МОм |

|

||

| D6 | FR107 |

|

||

| С6 | 220 пФ 1 кВ |

|

||

| R14 | 47 Ом, 2 Вт |

|

||

| С7 | 47 мк 25 В | ■ Цепь запуска | ||

| D14, D15 | 1N4148 | |||

| С4 | 0,1 мк275В | |||

| R2 | 2,7 к | |||

| D5 | HER103 | Выпрямитель цепи подзарядки накопительного конденсатора С7 i | ||

| R10 | 5,6 к | Времязадающая цепь | ||

| С10 | 0,01 мк | |||

| IC2 | TCET1108G | Оптрон | ||

| D8 | HER103 | Элементы схемы защиты от перегрузки по напряжению | ||

| ZD1 | BZX79-B15 | |||

| Q7 | 2SA733 | |||

| Q8 | 2SC945 | |||

| Т1 | EERL-28 | Импульсный трансформатор преобразователя (ТПИ) | ||

| Вторичные цепи | ||||

| D9 | 31DQ10 | Импульсный выпрямитель 12 В | ||

| D10 | SB540 | Импульсный выпрямитель 5 В | ||

| D12 | SR106 | Импульсный выпрямитель цепи питания стабилизатора напряжения -5 В | ||

| D13 | FR107 | Импульсный выпрямитель напряжения -40 В | ||

| IC3 | KIA431A | Каскад стабилизации (управляемый стабилитрон) | ||

| IC4 | UT587 | Стабилизатор напряжения 3,3 В | ||

| Q4 | 8550S | Стабилизатор напряжения -5 В | ||

| ZD2 | HZ6B2 | |||

| Q2 | CEP603AL | Ключи переключения режимов дежурный/рабочий |

|

|

| Q3 | 2SC945 | |||

| Q5 | 2SC945 |

|

||

| Q6 | 2SA733 |

|

||

Ограничение тока выходного ключа Q1

В этих режимах работы ИБП на выв. 8 микросхемы формируется напряжение 5 В и преобразователь работает на фиксированной частоте (приблизительно 58 кГц), которая определяется номиналами узлов времязадающей цепи СЮ

R10. Выработанные микросхемой положительные импульсы с выв. 6 IC1 через резисторы R8 и R7 прикладываются к затвору транзистора Q1 и открывают его. Так как транзистор имеет индуктивную нагрузку (обмотка 3–1 Т1), то его ток будет плавно нарастать, создавая на датчике тока R3A возрастающее положительное напряжение, которое через ограничивающий резистор R4 поступает на выв. 3 (вход C.S) микросхемы. Из

функциональной схемы МС IC1 SD3842A (см. рис. 5.3) видно, что к выв. 3 подключен неинвер-тирующий вход компаратора датчика тока (CURRENT SENSE COMPARATOR). На инвертирующий вход этого компаратора поступает управляющее напряжение с усилителя ошибки (ERROR AMP). Когда пилообразное напряжение от датчика тока превысит управляющее напряжение ошибки, на выходе компаратора появится уровень лог. «1», который, управляя последующими логическими схемами микросхемы, обеспечит запирание верхнего и отпирание нижнего транзистора тотемного выхода микросхемы. Напряжение на выходе IC1 SD3842A (выв. 6) уменьшится до нуля и выходной ключ Q1 (см. рис. 5.4) закроется. Описанный выше процесс обеспечивает ограничение тока выходного ключа Q1 в каждый период работы схемы, что предохраняет ключ от токовой перегрузки.

Вторичные цепи источника питания

Во вторичных цепях ИБП Billion с помощью импульсных выпрямителей формируются следующие напряжения:

• 12 В, выпрямитель — диод D9 (31DQ10);

• +5 В, выпрямитель — диод D10 (SB540);

• -40 В, выпрямитель — диод D13 (FR107);

• D12 (SR106) — выпрямитель для питания стабилизатора напряжения -5 В.

Причем первые три из этих напряжений обеспечивают питание соответствующих цепей проигрывателя, как в дежурном, так и в рабочем режимах.

В рабочем режиме на выв. 10 разъема CON2 поступает сигнал Active с уровнем лог. «1», открывающий через делитель R30 R31 ключевой транзистор Q3. Так как коллектор этого транзистора соединен непосредственно с затвором силового ключа Q2, он также откроется, и напряжение 5 В через этот ключ и дополнительные развязывающие фильтры поступит в цепи питания цифровой и аналоговой частей аппарата. Со стока транзистора Q2 питание поступит также на стабилизатор 3,3 В, который выполнен микросхеме IC4 (UT587). Необходимое выходное напряжение (3,3 В) этого стабилизатора задается делителем напряжения на резисторах R27 и R28.

Помимо этого напряжение 5 В со стока Q2 поступает на эмиттер р-п-р транзистора Q6. За счет смещения с делителя R35 R36 ключ на транзисторе Q6 открывается и обеспечивает отпирание ключа Q5, что, в свою очередь, обеспечивает работу параметрического стабилизатора напряжения -5 В на транзисторе Q4 и стабилитроне ZD2.

Групповая стабилизация выходных напряжений ИБП

Групповая стабилизация выходных напряжений ИБП осуществляется за счет петли управляющей ООС, в которую входят каскад стабилизации (управляемый стабилитрон) IC3 (KIA431A) и оптрон IC2 (TCET1108G). Анод светодиода опт-рона IC2 подключен к вторичному напряжению 12 В, а катод — к выходу управляемого стабилитрона IC3, т. е. ток через светодиод определяется выходным напряжением стабилитрона ЮЗ.

Предположим, выходные напряжения ИБП растут. Возрастет также напряжение на регулирующем входе стабилитрона IC3, которое поступает туда от источника 5 В через делитель R25 R22 R23. Выходное напряжение |СЗ растет, ток диода оптрона IC2 уменьшается, что приводит к увеличению сопротивления перехода транзистора оптрона и уменьшению постоянного напряжения на выв. 2 микросхемы IC1. Это напряжение усиливается и инвертируется усилителем ошибки (в составе микросхемы), что приводит к увеличению напряжения на выходе этого усилителя (выв. 1 на рис. 5.3). Как уже отмечалось, напряжение ошибки в микросхеме поступает на инвертирующий вход компаратора (CURRENT SENSE COMPARATOR), а на неинвертирующий вход этого компаратора поступает пилообразное напряжение от датчика тока. Теперь для запирания силового ключа понадобится несколько большее значение этого напряжения, а это значит, что выходной полевой транзистор Q1 будет открыт большее время. Это приведет к уменьшению скважности импульсов на выходе микросхемы и, следовательно, к уменьшению выходных напряжений ИБП до номинальных значений. Аналогично, но с точностью до «наоборот», работает схема в случае уменьшения выходных напряжений преобразователя БП.

Режим запуска

При включении DVD-проигрывателя в сеть конденсатор С7 ИБП заряжается от сети через помехоподавляющий фильтр и цепь запуска, состоящую из конденсатора С4, диодов D14, D15 и резистора R2. Когда напряжение на конденсаторе С7 и на выв. 7 микросхемы IC1 превысит пороговое значение (16 В), срабатывает схема UVLO микросхемы и напряжение с конденсатора С7 через эту схему поступает как питающее на основные узлы микросхемы. С выв. 8 IC1 опорное напряжение 5 В поступает на времязадаю-щую цепь R10 СЮ и на коллектор фототранзистора оптрона IC2. ИБП запускается в ТПИ Т1 возникают импульсы напряжения, которые с выв. 5 Т1 через дроссель L12 и диод D5 подзаряжают конденсатор С7, и блок питания плавно

входит в один из устойчивых режимов работы (рабочий или дежурный).

Причин, по которым может отсутствовать или быть недостаточной подзарядка конденсатора С7, может быть несколько:

• неисправна цепь запуска;

• значительно уменьшилась емкость конденсатора С7;

• перегружен ИБП;

• не работает или неустойчиво работает сам преобразователь ИБП.

Прерывистый режим

Если по какой либо причине конденсатор С7 не подзаряжается, напряжение на нем и на выв. 7 IC1 будет уменьшаться. Когда оно упадет до нижнего порогового уровня (10 В) схема UVLO в составе микросхемы IC1 отключит питание ряда узлов этой микросхемы. Исчезнет также напряжение на выв. 8, которым питались времязадающая цепь, фототранзистор оптрона IC2 и ИБП отключится. Его энергопотребление уменьшится до минимального уровня. Конденсатор С7 вновь будет заряжаться через цепь запуска до верхнего порогового напряжения (16 В), т. е. произойдет еще одна попытка запуска. Если причина отсутствия подзарядки конденсатора С7 не исчезла, то попытки запуска будут повторяться. Такой режим работы ИБП называют прерывистым. Он предохраняет ИБП и весь аппарат от возможной перегрузки. Этот режим обычно сопровождается характерным звуком — «цыканьем», которое издает импульсный трансформатор Т1.

Схема защиты от перегрузки по напряжению

Основой этой схемы является бистабильная ячейка на транзисторах разной проводимости Q7 и Q8. Эта схема широко применялась в отечественных телевизорах. Например, в сенсорном устройстве УСУ-15 популярного телевизора ЗУСЦТ таких ячеек было восемь. Она имеет два устойчивых состояния: оба транзистора заперты или оба транзистора открыты до насыщения. Кроме того, схема содержит отдельный импульсный выпрямитель на диоде D8 и пороговое устройство на стабилитроне ZD1.

При нормальной работе напряжение на выходе выпрямителя D8 — менее 15 В. Стабилитрон ZD1 и транзисторы ячейки заперты.

Когда напряжения ИБП повышаются выше нормы, напряжение на выходе выпрямителя D8 превысит уровень 15 В, стабилитрон ZD1 открывается и на базу Q8 поступает отпирающее напряжение. Транзистор Q8 открывается, обеспечивая отпирание транзистора Q7. При этом, за счёт того, что ток коллектора каждого из этих транзисторов является током базы другого транзистора, ячейка будет оставаться в открытом со—

стоянии, шунтируя выв. 1 микросхемы IC1 и блокируя ее работу.

Некоторые неисправности ИБП Billion и рекомендации по его ремонту

1. Если сгорел предохранитель F1, то следует проверить на пробой защитный варистор ZNR1, диоды моста и силовой транзистор Q1. Несколько реже пробивается конденсатор сглаживающего фильтра С5 и конденсаторы помехоподавляю-щего фильтра. При этом дефекте могут перегореть датчик тока R3A и ограничивающий резистор R55.

2. Тотемный выход микросхемы ШИМ контроллера (выв. 6) обычно выходит из строя по следующим причинам:

• завышено напряжение сети;

• неисправен оптрон IC2;

• неисправен управляемый стабилитрон IC3.

3. ИБП может не запускаться по следующим основным причинам:

• нет напряжения питания 300 В на конденсаторе сглаживающего фильтра С5;

оборван датчик тока R3A;

• в обрыве элементы цепи запуска: D14, D15, R2, С2. Причем, проверить исправность схемы запуска с 90% гарантией можно определить одним измерением, проверив напряжение 5 В на выв. 8 микросхемы IC1;

• обрыв узлов времязадающей цепи R10 СЮ;

• потеря емкости или утечка конденсатора С7;

• короткое замыкание во вторичных цепях ИБП;

• пробой одного их транзисторов схемы защиты от перегрузки по напряжению Q7, Q8 или стабилитрона ZD1;

• неисправность силового ключа Q1;

• неисправность микросхемы ШИМ контроллера.

4. ИБП может перейти в прерывистый режим по следующим причинам:

• перегрузка по потоку или короткое замыкание в нагрузках вторичных выпрямителей;

• обрыв элементов D5, L12 или обмотки 5–6 ТПИТ1;

• обрыв или потеря емкости конденсатора С7.

5. При отсутствии одного или нескольких выходных напряжений блока питания следует проверить коммутирующие ключи, стабилизаторы и выпрямители. Все эти цепи достаточно подробно рассмотрены.

Особенности импульсного блока питания ЕРМ

К сожалению, автору схему этого ИБП найти не удалось. Поэтому, сделаем небольшой обзор этого блока по имеющейся информации.

Примечание. Для обозначения позиционных номеров узлов фирма Philips использует четырехзначные числа. Например: 7101, 2107 и т. д. Подобные обозначения, с непривычки, крайне затрудняют как чтение принципиальных схем, так и поиск узлов на платах. Расшифруем эти обозначения. Первая цифра слева (старший разряд четырехзначного числа) обозначает тип детали. Хотя есть исключения, но, как правило, используется следующий код 1-й цифры:

' 1 — разъемы (соединители);

• 2 — конденсаторы; ' 3 — резисторы;

• 4 — перемычки (jampers);

• 5 — индуктивности, трансформаторы;

• 6 — диоды, диодные сборки, мосты, стабилитроны;

• 7 — транзисторы и микросхемы.

Следующая, вторая цифра, — это функциональный узел, к которому этот элемент относится. Здесь система прослеживается сложнее, но для узлов ИБП ЕРМ, которые расположены в первичной цепи 2-я цифра 1, а для узлов вторичной цепи — 2. Третья и четвертая цифры — это номер детали. Есть еще одна особенность. Некоторые проводники на принципиальных схемах сгруппированы в «жгуты», возле каждого проводника входящего или выходящего из такого виртуального жгута на схеме стоит маркировка. Так, например, в узле D2 можно найти проводник, обозначенный как D3–23. 23 — это номер проводника, а буквенно-цифровой код левее дефиса указывает узел, на схеме которого надо искать этот проводник там он будет обозначен как D2–23.

Основой ИБП типа ЕРМ также является об-ратноходовой импульсный преобразователь, который собран ШИМ контроллере 7101 серии TY720xx , выходном высоковольтном МДП транзисторе 7125 и импульсном трансформаторе с позиционным номером 5131. Частота преобразования 125 кГц задается конденсатором 2107, который подключен к выв. 5 микросхемы 7101. Оп-трон имеет позиционный номер 7102, а 7201 — это управляемый стабилитрон типа TL431. В качестве датчика тока выходного транзистора используются резисторы 3126, 3127 и 3128. Диоды сетевого выпрямителя имеют номера 6112...6115.

В целом схема и работа этого ИБП напоминает схему и работу ИБП Billion, поэтому методика ремонта этого блока аналогична предыдущему.

Узел привода с загрузчиком VAL6011

SD3.X LOADER ASSY — это узел привода с загрузчиком VAL6011 и главной платой. В состав узла узлу привода с загрузчиком VAL6011 (см. рис. 5.1) входят лазерная (оптическая) головка и три электродвигателя. Один из них (TRAY

MOTOR) обеспечивает загрузку и разгрузку диска (перемещение лотка с диском), другой (DISK MOTOR) — вращение диска (причем, в режиме воспроизведения с постоянной линейной скоростью), а третий (SLEDGE MOTOR) — перемещение и позиционирование лазерной головки. Лазерная (оптическая) головка (OPU — Optical Pick-Up) обеспечивает считывание информации с дисков. В оптической головке проигрывателя DVDQ50 используются два полупроводниковых лазерных диода на основе GaAIAs, один из которых имеет длину волны излучения 650 нм (для считывания DVD), а другой 780 нм (для VCD/CD). Числовая апертура 0,60 (DVD) и 0,45 (VCD/CD). Расходимость лучей лазеров составляет 60°. Лазерная (оптическая) головка содержит также две катушки, одна из которых обеспечивает ее радиальное смещение (ее сокращенно обозначают как RADIAL или tracking), что необходимо для точного позиционирования головки, а другая — фокусировку лучей (FOCUS).

Главная плата

Узел привода проигрывателя DVDQ50 может комплектоваться одной из двух разновидностей главных плат (MAINBOARD), которые отличаются типом микросхемы главного (ведущего) процессора (host processor). Позиционный номер этой микросхемы 7503. В этой позиции могут быть установлены БИС STi5508 (SD3.0) или STi5580 (SD3.1). Рассмотрим этот узел по функциональной схеме рис. 5.1.

Главную плату можно условно разделить на несколько функциональных узлов:

— аналоговый препроцессор;

— декодер аудио/видео;

— узел сервопроцессора;

— главный процессор.

Аналоговый препроцессор

Аналоговый препроцессор 7102 типа TZA1033 (DVDALAS2) обеспечивает:

— оптимальное, стабильное, раздельное питание каждого из полупроводниковых лазеров;

— усиление, обработку сигналов от фотодиодов лазерной головки, сложение этих сигналов и формирование на выходе ВЧ информационного сигнала (RF-сигнала или HF-сигнала);

— формирование НЧ сигналов для управления сервоприводами (LF-сигналов);

— раздельная программная установка коэффициентов усиления HF — и LF-сигналов, чем обеспечивается оптимальное качество считывания информации с разных дисков;

— формирование сигналов радиального слежения (автотрекинга) и фокусировки;

— LF-сигналы поступают на сервопроцессор МАСЕ2 7207 SAA7399, а HF-сигнал — на декодер 7311.

Декодер ВЧ сигнала

Декодер 7311 типа SAA7335HL/E/M2 обрабатывает ВЧ сигнал. Поскольку на рис. 5.1 эта микросхема «не раскрыта», то рассмотрим ее как по этому рисунку, так и по упрощенной функциональной схеме БИС SAA7335, которая изображена рис. 5.5.

Микросхема SAA7335HL/E/M2 обеспечивает:

— коррекцию симметрии HF-сигнала;

— фильтрацию шума;

— восстановление потока данных;

— синхронизацию блоков данных (frames — фреймов);

— демодуляцию 16-разрядных EFM+ или 14-разрядных EFM слов субкода DVD — и CD-сигналов соответственно, а также преобразование (декодирование) их в 8-разрядные цифровые сигналы;

— коррекцию ошибок и деперемежение, используя статическое ОЗУ (SRAM) 32 кБ на микросхеме 7310;

— формирование выходных сигналов данных (аудио и видео) для передачи их по цифровой мультимедийной шине l2S на главный процессор 7503.

Кроме того, микросхема 7311 формирует сигнал управления двигателем диска, который поступает на драйвер этого двигателя — микросхему 7304 типа BA6856FP. Для формирования этого сигнала на БИС 7311 через усилители микросхемы 7304 поступают сигналы от таходатчиков двигателя диска.

Декодер 7311 имеет две независимые шины управления: последовательную двухпроводную l2C и параллельную 8-разрядную. Через обе эти шины доступны все 32 8-разрядных регистра состояния и управления БИС.

Сервопроцессор

Сервопроцессор 7207 типа SAA7399 (МАСЕ2) — это основа сервопривода (см. рис. 5.1). Он обеспечивает, через микросхему драйверов 7103 (BA5938FM), управление двигателями TRAY MOTOR (загрузки-разгрузки) и SLEDGE MOTOR (перемещения и позиционирования лазерной головки), а также токами катушек радиального смещения (RADIAL) и фокусировки (FOCUS). От загрузчика на сервопроцессор поступает сигнал датчика TRAY-SWITCH.

Для обеспечения следящего режима управления электродвигателем SLEDGE MOTOR используются датчики Холла, сигналы от которых поступают на микросхему 7207 после усиления в микросхеме 7104 (LM833D).

Основа БИС 7207–8-разрядный микропроцессор 8051, работающий совместно с ПЗУ программ на микросхеме FLASH-памяти 7302 типа AM29F002 и обеспечивающий управление и обмен данными с БИС 7311. Микросхема 7201 типа 74HCT573D — это фиксатор адреса (ADDRESS LATCH), а 7208 типа MC33464N — схема сброса. Дуплексная асинхронная связь между сервопро-цессором и главным процессором (БИС 7503 STi5508 или STi5580) осуществляется по цифровой шине S2B (Serial to Basic).

Главный процессор

Главный процессор или, как его еще называют, ведущий процессор (host processor) — это БИС 7503 типа STJ5508 (SD3.0) или STi5580

Рис. 5.5. Упрощенная функциональная схема БИС SAA7335HUE/M2

(SD3.1). Этот процессор создан на микропроцессорном ядре ST20. Он работает совместно с тремя видами памяти: Flash-ROM, SDRAM и EEPROM.

Микросхема памяти Flash-ROM 7401 объемом 16 Мб используется в качестве ПЗУ программ DVD-проигрывателя. БИС 7503 обменивается информацией и управляет работой микросхемы Flash-ROM 7401 через три шины:

— SYSTEM DATA BUS;

— SYSTEM ADDRESS BUS;

— SYSTEM CONTROL BUS .

SDRAM — это синхронное динамическое ОЗУ. Оно обычно составлено из двух микросхем 7404 и 7405, каждая из которых имеет объем 16 Мб, но может использоваться и одна микросхема объемом 64 Мб. SDRAM выполняет две функции. Первая — это буфер сигнала изображения видеодекодера MPEG, а вторая — оперативное хранение кода исполняемых программ и данных, с которыми работают эти программы. Управление работой SDRAM и обмен данными с БИС 7503 осуществляется через SDRAM INTERFACE.

EEPROM (Electrically Erasable and Programmable Read Only Memory — электрически стираемое программируемое постоянное запоминающее устройство, ЭСППЗУ) — это энергонезависимая память, основное назначение которой — хранение данных при выключенном источнике питания. В проигрывателе DVDQ50 используется микросхема типа 24С32 объемом 32 кб, в которой хранятся все пользовательские и сервисные установки, включая код региона. БИС 7503 связана с микросхемой EEPROM по шине l2C.

Выделенные и преобразованные сигналы DVD, CD или CD-DA от БИС 7311 подаются на главный процессор по шине l2S, где они демультиплексируются и поступают на декодер MPEG (MPEG1 и MPEG2). Далее к видеосигналам добавляется служебная информация OSD (сигнал экранного меню) и они поступают на кодер PAL/NTSC (внутри микросхемы 7503), где преобразуются в следующие аналоговые сигналы соответствующих систем:

— сигналы основных цветов RGB или компонентные сигналы YUV;

— nU,TC(CVBS);

— сигналы S-VIDEO (яркостной — Y и сигнал цветности — С).

Эти сигналы поступают плату DTS BOARD или непосредственно на плату АЛ/ board.

На главной плате (моноплате) формируется трехуровневый сигнал, который подается на выв. 8 разъема1609 и обозначается как 0|6|12

(подробнее о особенностях использования этого сигнала см. в описании платы АЛ/ board).

Оцифрованные сигналы звука после демуль-типлексора поступают внутри микросхемы 7503 на аудиодекодер. Этот декодер поддерживает форматы аудиосигналов АС-3, MPEG1, MPEG2, PCM (Pulse Code Modulation — импульсно-кодо-вая модуляция) для БИС STi5508 и STi5580, а для БИС STi5580 — дополнительно форматы DTS и DVD-audio. Кроме того, микросхема может декодировать потоки данных в сигналы системы 5.1 или в два стереосигнала.

Шесть выходных цифровых мультиплексированных попарно звуковых сигналов (система 5.1) выводятся непосредственно или через плату DTS BOARD на плату АЛ/ board через следующие выводы разъемов главной платы:

— выв. 14 разъема 1603: левый и правый фронтальные каналы (PCMJDUT0);

— выв. 6 разъема 1604: центральный канал и канал сабвуфера (PCMJDUT1);

— выв. 4 разъема 1604: левый и правый тыловые каналы (PCM_OUT2).

Частоты дискретизации этих сигналов составляют 96, 48, 44,1 или 32 кГц.

Через контакт 21 разъема 1609 на плату DTS BOARD и далее на плату АЛ/ board выводится сигнал (цифровой поток данных) SPDIF. SPDIF (Sony-Philips Digital Interface Format) переводится как формат цифрового интерфейса фирм Sony и Philips.

Еще одна особенность БИС STi5508 и STi5580 заключается в том, что коррекция предыскажений (De-emphasis) сигналов звука осуществляется в цифровой форме непосредственно в этих БИС. Поэтому на плате АЛ/ board проигрывателя DVDQ50, который относят к третьему поколению DVD-проигрывателей, соответствующие цепи коррекции отсутствуют.

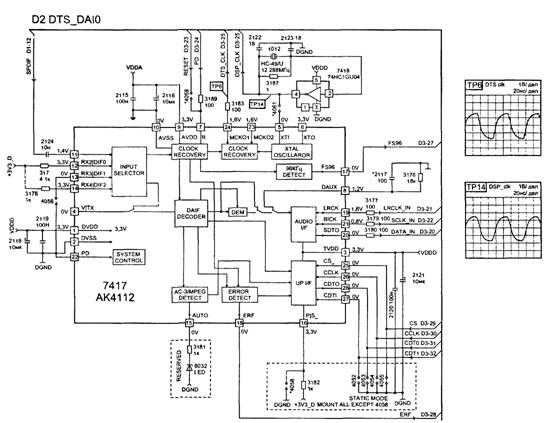

Плата DTS-BOARD

Плата DTS (Digital Theatre Sound) Board устанавливается между главной платой и платой АЛ/ Board только в проигрывателях с главным процессором 7503 типа STi5580. Он обеспечивает демодуляцию сигналов DTS и DVD-audio и получение полноценных цифровых аудиосигналов в системе 5.1. В процессе ремонта, для проверки работоспособности аппарата и дефектации платы DTS BOARD, ее можно отключить и соответствующие два шлейфа от главной платы включить непосредственно в разъемы платы АЛ/ board. Функциональная схема платы DTS-BOARD изображена на рис. 5.6, а принципиальная схема этой платы (в трех частях) показана на трех рисунках:

Рис. 5.6. Функциональная схема платы DTS-BOARD

— рис. 5.7 (узел D1 DTS-VIDEO);

— рис. 5.8 (узел D2 DTS-DAI0);

— рис. 5.9 (узел D3 DTS-DECODER).

На принципиальной схеме узла D1 DTS-VIDEO (рис. 5.7) можно увидеть два входных разъема с позиционными номерами 1000 и 1002 от главной платы (моноплаты) и два выходных разъема 1001 и 1003, в которые подключены шлейфы (ленточные кабеля) идущие на плату A/V board. В случае использования платы DTS перемычки 4007, 4008 и 4010– 4014 должны быть исключены.

Узел D1 DTS-VIDEO может содержать буферный усилитель сигнала яркости и активные матрицы для получения и цветоразностных сигналов R-Y (V) и В — Y (U) из сигналов основных цветов RGB, которые поступают от главной платы через контакты 5, 3 и 2 разъема 1002. Эти каскады собраны на микросхеме строенного ОУ 7401 типа AD8073. Для питания микросхемы AD8073 необходимо двухполярное питание ±5 В. Напряжение +5 В поступает с контакта 11 разъема 1002 (+5WID), а напряжение -5 В обеспечивает стабилизатор на микросхеме 7400 типа

MC79L05ABD со схемой включения на трех транзисторах 7000, 7001 и 7002.

Основой узла цифро-аналоговых входов и выходов D2 DTS-DAI0 (рис. 5.8) является микросхема 7417 типа АК4112А фирмы АКМ (Asahi Kasei Microsystems Co., Ltd). Узел также содержит кварцевый тактовый генератор 12,288 МГц на микросхеме 7418 типа 74HC1GU04. Микросхема 7417 — это приемник цифровых аудиосигналов (digital audio receiver — DIR), поддерживающий цифровые потоки с частотой выборки до 96 кГц (24 бит) и автоматическим обнаружением цифровых потоков не с импульсно-кодовой модуляцией (поп-РСМ). Назначение выводов микросхемы приведено в табл. 5,6.

Примечание: В обозначении выводов, помеченных в табл. 5.6 звездочкой (*), на схеме и в фирменном «даташите» [3] допущен ряд ошибок, что, в свою очередь, может привести к ошибкам при чтении схемы. Поэтому, в табл. 5.6 автором внесены обозначения в соответствии с принципиальной схемой рис. 5.8.

Следует отметить, что микросхема 7417 работает в параллельном режиме, т. к. на выв. 16 (PJS_) этой МС подан высокий уровень от источ—

Рис. 5.7. Принципиальная схема узла D1 DTS-VIDEO

Рис. 5.8. Принципиальная схема узла цифро-аналоговых входов и выходов D2 DTS-DAI0

Puc. 5.9. Принципиальная схема узла D3 DTS-DECODER

Таблица 5.6

Назначение выводов микросхемы 7417 типа АК4112

| Номер вывода | Обозначение | Назначение |

| 1 | DVDD | Напряжение питания цифровой части +3,3 В |

| 2 | DVSS | Общий цифровой части |

| 3 | TVDD | Напряжение питания +3,3 В или +5 В |

| 4 | V|TX | Выход флага достоверности в параллельном режиме или выход канала передачи данных в последовательном режиме |

| 5 | XTI | Вход сигнала от кварцевого резонатора |

| 6 | XTO | Выход сигнала на кварцевый резонатор |

| 7 | *R | Вход сброса и отключения микросхемы (активный уровень — низкий) |

| 8 | *DAUX | Вывод для подключения внешнего резистора 18 кОм |

| 9 | AVDD | Напряжение питания аналоговой части +3,3 В |

| 10 | AVSS | Общий аналоговой части |

| 11 | RX1 | Вход приема данных канала 1 (в последовательном режиме), а в параллельном режиме этот вход выбирается по умолчанию |

| ! 12 | RX2|DIF0 | Вход приема данных канала 2 в последовательном режиме или вход разряда 0 данных аудиосигнала в параллельном режиме |

| ; 13 | RX3|DIF1 | Вход приема данных канала 3 в последовательном режиме или вход разряда 1 данных аудиосигнала в параллельном режиме |

| 14 | RX4|DIF2 | Вход приема данных канала 4 в последовательном режиме или вход разряда 2 данных аудиосигнала в параллельном режиме |

| 15 | AUTO | Выход детектора опознавания импульсно-кодовой модуляции (РСМ) (высокий уровень РСМ нет, низкий — РСМ есть) |

| 16 | P|S_ | Вход выбора режимов (высокий уровень — паралельный режим, низкий — последовательный) |

| 17 | FS96 | Выход частоты выборки 96 кГц |

| 18 | ERF | Выход детектора ошибки (низкий уровень — нет ошибки, высокий — есть ошибка) |

| 19 | LRCK | Выход канальных тактовых импульсов |

| 20 | SDTO | Выход последовательных аудиоданных |

| 21 | BICK | Выход тактовых импульсов последовательных аудиоданных |

| 22 | *PD_ | Вход дополнительных данных |

| 23 | MCK02 | Выход главных тактовых импульсов 2 |

| 24 | MCK01 | Выход главных тактовых импульсов 1 |

| 25 | CS. | Вход выбора кристалла в последовательном режиме или выход выбора выходных тактовых импульсов 0 в параллельном режиме |

| 26 | CCLK | Вход тактовых импульсов управления в последовательном режиме или выход выбора выходных тактовых импульсов 1 в параллельном режиме |

|

27

|

CDTI | Вход данных управления в последовательном режиме или вход 0 главных тактовых импульсов в параллельном режиме |

|

28

|

CDTO | Выход данных управления в последовательном режиме или вход 1 главных тактовых импульсов в параллельном режиме |

Узел D3 DTS-DECODER собран на базе БИС цифрового сигнального процессора 7406 типа DSP56366 (рис. 5.9). 24-разрядный цифровой сигнальный процессор DSP56366 выполнен в 144-выводном корпусе LQFP. Приблизительно четвертая часть из них — это выводы для подключения напряжений питания и общего прово—

да. Кроме того, в данном аппарате не используются цифровые аудиосигналы в параллельном коде. В этой связи, остались незадействованны-ми две параллельные шины (рис. 5.9): 18-разрядная адресная (PORT A External Address Bus) и 24-разрядная шина данных (PORT A External Data Bus).

Выходной цифровой аудиосигнал микросхемы 7417 снимается с выв. 20 (SDTO) и поступает на выв. 10 БИС DTS-декодера 7406. В режиме обработки DTS этот сигнал будет не в формате

импульсно-кодовой модуляции (поп-РСМ). На БИС 7406 с микросхемы 7417 поступает также ряд тактовых и вспомогательных сигналов. Сигнал, поступивший на выв. 10 7406, демодулиру-ется этой микросхемой и в виде шести выходных цифровых мультиплексированных попарно сигналов звука (5.1) выводится через выв. 4, 5 и 6 7406 на электронные коммутаторы. В качестве электронных коммутаторов используются микросхемы 7407 и 7408 типа 74HCT157D.

В режиме обработки DTS на коммутаторы поступают также следующие тактовые сигналы:

— на выв. 13 7407 от выв. 24 7417 — тактовый сигнал DTS_CLK,

— на выв. 3 7407 от выв. 14 БИС 7406 — тактовый сигнал SCLK_OUT,

Для коммутации этих сигналов на плату A/V board на выв. 1 микросхем 7407 и 7408 поступают уровни лог. «1» от выв. 32 7406. При подаче лог. «0» на эти выводы на плату A/V board будут коммутироваться соответствующие цифровые мультиплексированные попарно сигналы звука и тактовые импульсы, поступившие на входы микросхем 7407 и 7408 от главной платы.

В узел D3 DTS-DECODER входят также стабилизатор +3,3 В на микросхеме 7409 типа LD1117DT33 и, если не установлена перемычка 4025, то и стабилизатор +1,8 В на микросхеме 7410 типа LD1117DT25.

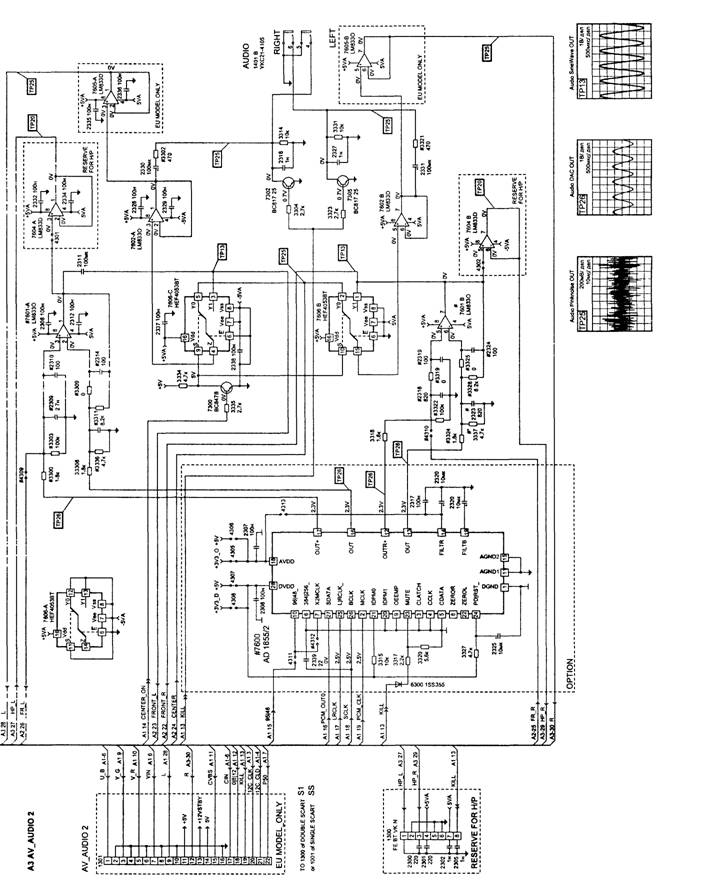

Плата A/V Board

Производитель делит эту плату на три узла:

— А1 AV_VIDEO (рис. 5.10);

— А2 AV_AUDI01 (рис. 5.11);

— A3 AV_AUDI02 (рис. 5.12).

На узел А1 AV_VIDEO через разъемы 1100 и 1101 (см. рис. 5.10) поступают шесть видеосигналов:

— nUTC(CVBS);

— два формата S-VIDEO (яркостной YIN и сигнал цветности CIN);

— три компонентных (U_B — цветоразностный или основной синего, V_R — цветоразностный или основной красного и Y_G — яркостной или основной зеленого).

Причем сигналы основных цветов (RGB) подаются на эту плату только в проигрывателях, предназначенных для Европы.

Эти сигналы попадают на входы шести буферных видеоусилителей, которые собраны на микросхеме 7400 типа LA7109, где они усиливаются на 6 дБ и поступают на соответствующие выходные разъемы. В некоторых проигрывателях на выв. 3, 13, 20 и 30 микросхемы 7400 поступает сигнал VIDEO-MUTE (активный уро—

вень — низкий), который блокирует ее работу, но в большинстве аппаратов эти выводы подключены к источнику +5 В через перемычку 4108.

Назначение выводов разъема S-VIDEO 1402 типа TCS79 приведено в табл. 5.7.

Таблица 5.7

Назначение выводов разъема S-VIDEO 1402 типа (TCS7S)

| Выводы | Назначение |

| 1 | Общий |

| 2 | |

| 3 | Выход сигнала яркости (Y) |

| 4 | Выход сигнала цветности (С) и сигнала управления |

Цифровой аудиосигнал (цифровой поток аудиоданных) SPDIF с контакта 21 разъема 1101 через трансформатор гальванической развязки 5103 поступает на коаксиальный разъем 1404, а также на разъем OPTICAL, в который встроен драйвер 7402 GP1F32T с излучающим ИК диодом.

Цифровые сигналы звука (PCM_OUT0, PCM_OUT1 и PCM_OUT2) и три тактовых сигнала с разъемов подаются на неинвертирующую буферную микросхему 7403 типа 74F365D. Каждый из выходов этой микросхемы может находиться в одном из трех состояний: лог. «0», лог. «1» или высокоимпедансном состоянии. Логические уровни сигналов на входах и выходах микросхемы 7403 типа 74F365D приведены в табл. 5.8.

Таблица 5.8

Логические уровни сигналов на входах и выходах микросхемы 74F365D

| Входы | Выход | ||

| 0Ё1(выв 1) | 0Ё2(выв 15) | 1(выв 2,4,6, 10,12,14) | 0(выв 3,5,7,9, 11, 13) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| X | 1 | X | Z |

| 1 | X | X | Z |

Поскольку, в схеме рис. 5 10 выв 1 и 15 заземлены, то входные и выходные сигналы могут

принимать только те значения, которые выделены в табл. 5 8 жирным шрифтом.

Рис. 5.11. Принципиальная схема узла А2 AV_AUDI01

Рис. 5.12. Принципиальная схема узла A3 AV_AUDIQ2

Выходные сигналы с буфера 7403 74F365D поступают на ЦАПы узла А2 AV_AUDIOL

Узел А2 AV_AUDI01 (рис. 5.11) содержит три ЦАП, четыре усилителя выходных сигналов и шесть транзисторных ключей, а также шесть выходных аудиоразъемов.

ЦАПы находятся в микросхемах 7500, 7502 и 7504 типа UDA1334TS. В каждой из этих микросхем до ЦАП осуществляется интерполирование сигнала и «формовка шума» (Noise Shaping). Разновидности сигналов, которые обрабатываются этой микросхемой определяются логическими уровнями на выв. 7 и 11. В нашем случае оба эти вывода подсоединены на корпус. Входной цифровой мультиплексированный сигнал поступает на выв. 3 микросхемы UDA1334TS, а два аналоговых снимаются с выв. 14 и 16. Отключены также функции MUTE и DE-EMPHASIS (коррекция предыскажений), т. к. выв. 8 и 9 также подсоединены на корпус. Микросхема 7500 преобразует цифровой сигнал PCM_OUT0 в аналоговые левый и правый фронтальные. 7502 преобразует цифровой сигнал PCM_OUT1 в аналоговые центральный сигнал и сигнал сабвуфера, а 7504 цифровой сигнал PCM_OUT2 преобразует в левый и правый тыловые сигналы.

Сигналы центрального, тыловых, и сабвуферного каналов усиливаются одним из усилителей микросхемы счетверенного ОУ 7503 типа LM833D и поступают на соответствующий выходной разъем.

Фронтальные сигналы с выходов микросхемы 7500 поступают в узел A3 AV_AUDI02, а затем после обработки возвращаются обратно в узел А2 AV_AUDI01 и поступают на соответствующие выходные разъемы. Шесть транзисторных ключей 7200...7205 блокируют выходы системы 5.1 (разъемы 1400) по команде KILL.

Узел A3 AV_AUDI02 (рис. 5.12) не очень сложен, но крайне запутан, т. к. претерпел массу мелких модернизаций, каждую из которых производители решили отобразить на одной принципиальной схеме.

Фронтальные сигналы FR_R и FR_L от узла А1 поступают на ОУ 7601-В и 7601-А (1/2 микросхемы LM833D) соответственно. После усиления эти сигналы опять в узел А1. Кроме того, при работе в режиме стерео эти сигналы через коммутаторы 7606-В и 7606-С микросхемы HEF4053BT поступают на повторители 7602-В и 7602-А соответственно, а затем, с выхода повторителей на выходные разъемы стерео 1401-В. При работе в режиме моно по команде CENTER_ON ключ 7300 переключит коммутаторы 7606-В и 7606-С в такое положение, что на повторители 7602-В и 7602-А, а значит и на выходные разъемы 1401-В поступит сигнал CENTER.

В некоторых модификациях проигрывателя на А1 отсутствует микросхема ЦАП 7500, в этих аппаратах в узле А2 устанавливается ЦАП на микросхеме 7600 типа AD1855/2.

Плата P.SCAN BOARD

Полное название этой платы PROGRESSIVE SCAN BOARD, что переводится как «Плата прогрессивной (построчной) развертки». Плата преобразует стандартные цифровые YUV видеосигналы в аналоговые ТВ сигналы с удвоенным количеством строк. Она устанавливается в качестве опции (ее отсутствие скорее норма, чем исключение).

Выходные сигналы платы P.SCAN BOARD формируются также в формате YUV. Но в проигрывателе DVDQ50 такое преобразование осуществляется только для американского стандарта в аппаратах выпущенных не для Европы. В этом случае чересстрочный сигнал 525 строк преобразуется в прогрессивный (построчный) сигнал с удвоенным количеством строк.

Плата P.SCAN BOARD устанавливается также в проигрыватели DVDQ50 предназначенные и для европейского рынка, но обеспечивает только получение выходных чересстрочных аналоговых YUV-сигналов без удвоения числа строк. Поэтому плата P.SCAN BOARD изготавливается в двух вариантах: для европейской и не европейской версии проигрывателя DVDQ50.

Функциональная схема обеих версий платы P.SCAN BOARD изображена на рис. 5.13.

Не европейская версия платы P.SCAN BOARD (PROGRESSIVE YUV), показанная в верхней части рис. 5.13, комплектуется БИС преобразователя видеоформата 7100 типа FLI2200 с микросхемой памяти 7101 типа

MT48LC2M32B2TG и кодера с тремя одиннадцатиразрядными выходными ЦАП на БИС 7202 типа ADV7196A.

Европейская версия платы P.SCAN BOARD (HIGH QUALITY INTERLACED YUV), показанная в нижней части рис. 5.13, не содержит перечисленных выше микросхем, вместо которых установлена одна БИС 7203 типа ADV7190KST. Эта БИС представляет собой цифровой видеокодер, который преобразует цифровой 8– или 16-разрядный компонентный видеосигнал YUV формата 4:2:2 (в соответствии с CCIR-601/656) в стандартные аналоговые телевизионные сигналы с улучшенными параметрами.

Принципиальная схема платы P.SCAN BOARD (обе версии сразу) разделена на три узла:

— Р1 — узел удвоения количества строк (P-scan_LineDoubler), см. рис 5.14;

— Р2 — узел формирования аналоговых сигналов YUV высокого качества (High Quality YUV), см. рис. 5.15;

— РЗ — узел кодера (P_scan_Encoder), см. рис. 5.16.

Основные компоненты неевропейской версии платы P.SCAN BOARD находятся в узлах Р1 (рис. 5.14) и РЗ (рис.5.16), а европейской — в Р2 (рис. 5.15). Поскольку для нас более актуальна, именно, европейская версия платы P.SCAN BOARD рассмотрим ее более подробно.

8-разрядный цифровой сигнал YUV поступает по шлейфу от главной платы (MONO BOARD) на разъем 1002 (контаткты 2, 4, 6, 8, 10, 12, 14, 16)

платы P.SCAN BOARD (см. рис. 5.15), а далее заводятся в БИС видеокодера 7203 типа ADV7190KST через выв. 1...8 (младшие разряды входного порта Р0...Р7). На контакты 18 и 20 этого разъема поступают строчные (HSYNC) и кадровые (VSYNC_MONO) импульсы синхронизации, а на контакт 22 — тактовые импульсы частотой 27 МГц (сигнал 27M_CLK). Сигнал HSYNC поступает на выв. 19, VSYNC_MONO — на выв. 20, а сигнал 27M_CLK — на выв. 27 этой микросхемы. Микросхема 7203 понижает шумы, уменьшая их амплитуду и увеличивая их частоту в выходном аналоговом сигнале, за счет передискретизации и использования технологии Digital Noise Reduction.

Рис. 5.13. Функциональная схема платы P.SCAN BOARD

Видеокодер микросхемы ADV7190KST содержит шесть 10– разрядных ЦАП с передискретизацией (Oversampling) 54 МГц, из которых в данной схеме используются только три РЗ (рис 5 16). Выходные аналоговые компонентные видеосигналы с выходов видеокодера через ФНЧ поступают на выходные ВУ на микросхемах 7204, 7205 и 7207 типа AD8061 При этом яркостной сигнал Y снимается с выв 45, цветоразностный сигнал синего U (B-Y) — с выв. 44, а цветоразностный сигнал красного V

(R-Y) — с выв 41 микросхемы 7203. С выходов микросхем 7204, 7205 и 7207 сигналы Y, U и V поступают на разъемы 1003А, 1003В и 1003С, которые называют и обозначают на задней стенке как PROGRESSIVE SCAN OUT, Y, Pb/Cb, Pr/Cr.

Для питания микросхем напряжениями +3,3 и +2,5 В используются интегральные стабилизаторы на микросхемах 7201 или 7102 (LD1117DT33) и 7103 (LD1117DT25). Последние две микросхемы входят в состав узла Р1 P-scan_LineDoubler

Рис. 5.14. Принципиальная схема узла Р1 P-scan_Line Doubter

(см. рис. 5.14). Кроме того, для формирования синхронизирующего сигнала VSYNC, который необходим для БИС 7100 FLI2200 (см. схему узла Р1 P-scan_l_ineDoubler рис. 5.14), используется

формирователь на D-триггере 7200-А (1/2 микросхемы типа 74LVT74) и вентиле 7206-А (1/4 МС 74LVT86DB). Этот формирователь изображен на схеме узла Р2 High Quality YUV (см. (5.15).

Рис. 5.14. (продолжение) Принципиальная схема узла Р1 P-scan_Line Doubter

Рис 5 16 Принципиальная схема узла РЗ P-scan_Encoder

Плата С CONTROL PANEL

Плата С CONTROL PANEL на схеме соединений DVD-проигрывателя DVDQ50 (рис 5 2) обозначена как [1002В] FRONTB Принципиальная схема этой платы изображена на рис 5 17

Плата С CONTROL PANEL содержит

— светодиод-индикатор дежурного режима 6200 типа LTL-2R7TWK, которым непосредственно управляет транзисторный ключ 7109 ВС857В,

— фотоприемник системы дистанционного управления 7100 типа TSOP2236,

— бипер (Beeper) состоящий из пьезокапсуля 1132 типа РКМ и драйвера на транзисторе 7110 типа ВС817–25,

— кнопки локальной клавиатуры 1102 (Next), 1103 (Prev), 1111 (Standby)

Плата С CONTROL PANEL достаточно проста и дополнительного объяснения не требует

Плата D DISPLAY PANEL

Плата D DISPLAY PANEL на схеме соединений (рис 5 2) обозначена как [1002А] FRONTA Основой этой платы является процессор управления 7104 типа ТМР87РМ48 (рис 5 18)

Процессор управления 7104 ТМР87РМ48 является ведомым для главного процессора (host processor) БИС 7503 типа STi5508 (главная плата SD3 0) или STi5580 (главная плата SD3 1) Он обменивается информацией с главным процессо—

Puc 5 17 Принципиальная схема платы С CONTROL PANEL

ром и памятью по шине PC (выв. 18 и 19 БИС 7104).

Основное назначение процессора управления следующее:

— сканирование локальной клавиатуры и LCD-индикатора;

— декодирование и выполнение команд пришедших от ИК-приемника или локальной клавиатуры.

Процессор управления 7104 ТМР87РМ48 формирует также команду включения рабочего режима и перевода аппарата в дежурный режим (выв. 15), управляет (через выв. 27) ключом 7107, который в рабочем режиме включает све-тодиод подсветки LCD-индикатора. Обеспечивает включение индикатора дежурного режима на плате С CONTROL PANEL, вырабатывая в этом режиме низкий потенциал на выводе 8.

Подробное назначение выводов процессора управления 7104 (ТМР87РМ48) представлено в табл. 5.9.

Таблица 5.9

Назначение выводов процессора ТМР87РМ48

| Номер вывода | Обозначение* |

|

Назначение | |

| 1 VSS | Корпус | |||

| 2 | хот | Кварцевый резонатор 8 МГц | ||

| 3 | XIN | |||

| 4 | RESET | Вход сброса | ||

| 5 |

|

Г1ортР2 | Выход интерфейса Р50 | |

| 6 |

|

Не используется | ||

| 7 | TEST | Вход сигнала за | водского тестирования | |

| 8 |

|

Г1ортР2 | Выход управления индикатором дежурного режима | |

| 9 |

|

Порт Р1 | Не используется | |

| 10 |

|

Не используется | ||

| 11 |

|

Вход интерфейса Р50 | ||

| i 12 |

|

Выход сигнала Beeper | ||

| 13 |

|

Не используется | ||

| 14 |

|

Не используется | ||

| 15 |

|

Выход команды вкл /выкл. (дежурный/рабочий режимы) | ||

| 16 |

|

Не используется | ||

| 17 |

|

Порт Р4 | Не используется | |

| 18 |

|

Линия SCL шины l2C | ||

| 19 |

|

Линия SDA шины l2C | ||

| 20 |

|

Не используется | ||

| 21 |

|

Не используется | ||

| 22 |

|

Не используется | ||

| 23 |

|

Порт Р8 | Порт не используется | |

| 24 |

|

|

||

| 25 |

|

|

||

| 26 |

|

|

||

| 27 |

|

Порт Р5 | Выход команды включения подсветки LCD-индикатора | |

| 28 |

|

Не используется | ||

| 29 |

|

Вход кода от ИК-приемника | ||

| 30 | VASS | Корпус | ||

| Номер вывода | Обозначение | Назначение | ||

| 31 | VAREF | Напряжение питания +5 В | ||

| 32 | VDD |

|

||

| 33 |

|

ПортРб | Не используется | |

| 34 |

|

Выходы опроса клавиатуры | ||

| 35 |

|

|||

| 36 |

|

|||

| 37 |

|

Не используется | ||

| 38 |

|

Не используется | ||

| 39 |

|

Не используется | ||

| 40 |

|

Не используется | ||

| 41 |

|

Порт Р7 | Вход опроса клавиатуры | |

| 42 |

|

Не используется | ||

| 43 |

|

Входы опроса клавиатуры 1 | ||

| 44 |

|

|||

| 45 |

|

Не используется 1 | ||

| 46 |

|

Не используется | ||

| 47 |

|

Не используется | ||

| 48 |

|

Не используется | ||

| 49 |

|

ПортРО | Порт не используется | |

| 50 |

|

|||

| 51 |

|

|||

| 52 |

|

|||

| 53 |

|

|||

| 54 |

|

|||

| 55 |

|

|||

| 56 |

|

|||

| 57 |

|

ПортРЗ | Не используется | |

| 58 |

|

Не используется | ||

| 59 |

|

Не используется | ||

| 60 |

|

Выводы управления LCD-индикатором | ||

| 61 |

|

|||

| 62 |

|

|||

| 63 |

|

|||

| 64 |

|

На транзисторе 7108 собрана схема сброса процессора управления 7104.

БИС 7104 ТМР87РМ48 через выв. 5 и 11 управляет работой двунаправленного последовательного интерфейса Р50 для связи между видеооборудованием. В проигрывателях с разъемами SCART под интерфейс Р50 отведен контакт 10 этого разъема, а в остальных — разъем 1405, расположенный в узле А1 AV_VIDEO (см. рис. 5.10). Транзистор 7101 — это формирователь сигнала интерфейса Р50.

Остальные особенности видны из схемы (рис. 5.18) и табл. 5.9.

Тестирование DVD-проигрывателя DVDQ50 с помощью встроенного программного обеспечения

Особенности программного обеспечения DVD-проигрывателя DVDQ50

Программное обеспечение (ПО) DVD-проигрывателя DVDQ50 имеет встроенную систему диагностики (Diagnostic Software), основой которой является несколько тестовых программ — ядер (Nucleuses), которые объединяются в целевые последовательно исполняемые группы — сценарии (Scripts). Для выполнения некоторых сценариев нет необходимости в дополнительном оборудовании, и даже, в разборке аппарата. Для выполнения других сценариев необходимо подключение телевизора, внешних шестиканальных усилителей (УМЗЧ) и акустических систем. Может понадобиться, также, частичная разборка аппарата для того, чтобы была возможность проверить правильность работы механических узлов. ПО позволяет просматривать регистры ошибок и биты ошибок, что облегчает конечный поиск неисправностей проигрывателя DVDQ50.

Начальная диагностика

Диагностику следует начинать со сценария распределения (Dealer Script). Начальная диагностика может производиться автономно, без подключения телевизора, УМЗЧ и любого иного оборудования. Сценарий Dealer Script состоит из шести ядер и позволяет проверить память и интерфейс l2C (см. табл. 5.10).

Таблица 5.10

Назначения и коды ядер сценария Dealer Script

| Обозначение ядра | Назначение ядра | Код |

| PapChksFI | Вычисление и проверка контрольной суммы FLASH-памяти | 06 |

| Papl2cDisp | Проверка шины l2C ведомого процессора 7104 ТМР87РМ48 на плате D DISPLAY PANEL | 05 |

| i PapS2bEcho | Проверка шины l2C схемы управления приводом | 04 |

| | Papl2cNvram | Проверка шины гС энергонезависимой памяти | 03 |

| PapNvramWrR | Проверочный тест всех ячеек энергонезависимой памяти | 02 |

| CompSdramWrR | Проверочный тест всех ячеек ОЗУ микросхем 7404 и 7405 (главная плата) | 01 |

— выключить DVD-проигрыватель сетевой кнопкой;

— одновременно нажав кнопки <EJECT> и <PLAY/PAUSE> и удерживая их, включить проигрыватель.

Ядра сценария будут поочередно выполняться в последовательности: от ядра с большим кодом к ядру с меньшим кодом. В процессе выполнения того или иного ядра на индикаторе (LCD-дисплее) проигрывателя будет высвечиваться код ядра (см. рис. 5.19а) и состояние BUSY — «занято». Если сценарий выполнен без сбоев, то индикатор высветит сообщение PASS — «прошло» (см. рис. 5.196), в противном случае на индикаторе -появится сообщение об ошибке — ERROR (см. рис. 5.19в). Для прекращения работы сценария Dealer Script необходимо отключить сеть.

Рис. 5.19. Сообщения на индикаторе при выполнении сценария Dealer Script

Комплексная проверка проигрывателя. Сценарий Player Script

Сценарий Player Script обеспечивает проверку трех основных составляющих DVD-проигрывателя DVDQ50:

— платы дисплея (D DISPLAY PANEL);

— цифровой части главной платы (моноплаты);

— сервочасти главной платы (моноплаты) и узла привода.

Сценарий Player Script предусматривает два этапа проверки. Первый этап интерактивный, для выполнения команд (ядер) которого необходимо вмешательство ремонтника, а второй — циклический тест (LOOP TEST). Он выполняется непрерывно, без вмешательства человека, до момента отключения питания ядро за ядром в следующей последовательности:

— VideoScartSwComm;

— PapChksFlash;

— Papl2cNvram;

— CompSdramWrR;

— PapS2bEcho;

— Papl2cDisp.

Почти все эти ядра входят в сценарий Dealer Script (см. табл. 7)

Активация, блок-схема работы и выход из сценария Player Script показаны на рис. 5.20.

Наименования и обозначения ядер (тестов) на рисунке представлены без дополнительного перевода.

Для всех версий ПО, начиная с DSW 1.6 и более новых, перед выполнением интерактивной части сценария Player Script, на LCD-дисплее (индикаторе) выдается сообщение о версии ПО (см. рис. 5.21).

Для продолжения выполнения следующих шагов проверки необходимо нажать кнопку <PLAY/PAUSE>.

А теперь остановимся подробнее на каждой из трех составляющих сценария Player Script.

Тест платы дисплея

Тест платы дисплея содержит пять тестов, каждый из которых выполняется соответствующим ядром сценария Player Script (см. также рис. 5.20):

— тест дисплея (DISPLAY TEST) — ядро Disp-Display (30а);

— тест светодиодов (LED TEST) — ядро DispLed (29);

— тест клавиатуры (KEYBOARD TEST) — ядро DispKeyb (27);

— тест пульта дистанционного управления (REMOTE CONTROL) — ядро DispRc (28);

— тест отклика последовательного интерфейса Р50 «Easylink» (Р50 LOOP BACK TEST) — ядро DispP50 (60).

Тест дисплея (DISPLAY TEST) позволяет проверить срабатывание всех сегментов и качество подсветки индикатора (LCD-дисплея), последовательно формируя три «картинки» при нажатии на кнопки, как показано на рис. 5.22. Если соответствующие сегменты подсвечены равномерно, то следует нажать кнопку <EJECT>, а если нет, то — <STOP>. При этом яркость подсветки будет изменяться в каждом цикле. При получении оптимальной яркости необходимо нажать кнопку <PLAY/PAUSE> для активации следующего теста.

Кроме того, при неправильном включении сегментов индикатора, по характеру изменений «картинок», показанных на рис. 5.22, можно судить о причинах дефекта, что упрощает дальнейший поиск дефектной детали.

Если нажать кнопку <PLAY/PAUSE> не завершив цикл, то результат проверки фиксируется, как негативный (ложный) — FALSE.

Рис. 5.20. Активация, блок-схема работы и выход из сценария Player Script

Рис. 5.22. Блок-схема теста дисплея

Тест светодиодов (LED TEST) позволяет визуально проверить свечение светодиодов. Если светодиоды исправны (ответ «Да»), то следует нажать кнопку <EJECT>, а если нет (ответ «Нет»), то следует нажать кнопку <STOP>. Для активации следующего теста необходимо нажать кнопку <PLAY/PAUSE>. При нажатии этой кнопки до окончания теста ПО воспримет его как позитивный результат (PASS).

Тест клавиатуры (KEYBOARD TEST) позволяет проверить коды всех кнопок локальной клавиатуры (см. табл. 5.11).

Таблица 5.11

Коды кнопок локальной клавиатуры

Необходимо поочередно нажать все кнопки локальной клавиатуры проигрывателя при этом на индикаторе правее ТВ будут появляться коды кнопок (один разряд) и количество нажатий на каждую из них (один шестнадцатеричный разряд для кнопки). Полученные двухразрядные коды по мере нажатия на кнопки будут перемещаться справа налево. Если на какую-либо кнопку нажали несколько раз, на дисплее будут отображаться все нажатия. При этом каждое последующее сообщение на дисплее будет иметь тот же код

кнопки, но увеличенный на 1 показатель числа нажатий. Процесс заканчивается заполнением индикатора. Если, при этом, хотя бы одна из кнопок нажата не была, то тест будет считаться не выполненным и на дисплее появится сообщение, как на рис. 5.23а. Если тест выполнен правильно и коды кнопок совпадают с табл. 8, то на дисплее появится сообщение, как на рис. 5.236. Одно из этих сообщений появится при нажатии на кнопку <PLAY/PAUSE> в течение 1 сек и более. Повторное нажатие на эту кнопку активирует следующий тест.

Рис. 5.23. Сообщение на индикаторе о прохождении теста клавиатуры

Тест пульта дистанционного управления (REMOTE CONTROL) позволяет проверить коды всех кнопок пульта ДУ (см. табл. 5.12).

Эта проверка осуществляется аналогично предыдущей. Только сообщения на LCD-дисплее выглядит несколько иначе (см. рис. 5.24).

Таблица 5.12

Коды кнопок пульта ДУ

| Кнопка | 16-ричныйкод | ||

| STANDBY | ОС | ||

| STOP | 31 | ||

| PLAY | 2C | ||

| PLAY BACKWARD | 2D | ||

| PAUSE | 30 | ||

| STEP FORWARD | F6 | ||

| STEP BACKWARD | F5 | ||

| FORWARD | 28 | ||

| FORWARD 4X | DF | ||

| FORWARD 8X | E0 | ||

| BACKWARD | 29 | ||

| BACKWARD 4X | DE | ||

| BACKWARD 8X | DD | ||

| SLOW | 22 | ||

| SLOW 2 | D9 | ||

| SLOW BACKWARD |

23

|

||

| SLOW BACKWARD | DA | ||

| NEXT | 20 | ||

| PREVIOUS | 21 | ||

| CURSOR UP | 58 | ||

| CURSOR DOWN | 59 | ||

| CURSOR LEFT | 5A | ||

| CURSOR RIGHT | 5B | ||

| OK | 5C | ||

| Кнопка | 16-ричный код | ||

| 0 | 0 | ||

| 1 | 1 | ||

| 2 | 2 | ||

| 3 | 3 | ||

| 4 | 4 | ||

| 5 | 5 | ||

| 6 | 6 | ||

| 7 | 7 | ||

| 8 | 8 | ||

| 9 | 9 | ||

| TOGGLE | C8 | ||

| ANGLE | 85 | ||

| AUDIO | 4E | ||

| SUBTITLES | 4B | ||

| SUBTITLE ON/OFF | E3 | ||

| ROOT MENU | 54 | ||

| TITLE MENU | 71 | ||

| MENU | D1 | ||

| SETUP MENU | 82 | ||

| OSD ON/OFF | F | ||

| RETURN | 83 | ||

|

RESUME

|

D7 | ||

|

SCAN

|

2A | ||

| SHUFFLE | 1С | ||

| REPEAT | 1D | ||

| A/B REPEAT | 3B | ||

| TOGGLE SCART | 43 | ||

| OPEN/CLOSE | 42 | ||

| FTS | FB | ||

| KARAOKE | E4 | ||

| OPTION | FA | ||

Рис. 5.24. Сообщение на индикаторе при проверке кнопок ДУ

Две буквы RC на рис. 5.24 слева показывают, что это тест пульта ДУ (REMOTE CONTROL). Крайнее справа 16-ричное 2-разрядное число (23) — это код кнопки. В дальнейшем, для экономии места, сообщения на индикаторе будут приводиться не в виде рисунка, а обычной надписью.

Тест отклика последовательного интерфейса Р50 «Easylink»

Этот тест не является обязательным. Тем более, что далеко не во всех аппаратах имеется интерфейс Р50 «Easylink». Поэтому, при появлении на индикаторе сообщения: «Р50 TEST», необходимо решить: проводить этот тест или нет. Если тест решили запустить, то следует нажать кнопку <EJECT>, а если нет — кнопку <STOP>.

В первом случае результатом проверки будет сообщение «Р50 PASS», если тест дал положительный результат и «Р50 FAIL», если результат отрицательный. Для перехода к выполнению следующего теста нажать кнопку

<PLAY/PAUSE>.

Тест цифровой части главной платы (моноплаты)

Тест цифровой части главной платы (моноплаты) содержит пять тестов, каждый из которых выполняется соответствующим ядром сценария Player Script (см. рис. 5.20):

— видеотест (PICTURE TEST) — ядро VideoCol-DencOn (23а);

— 1-й звуковой тест (SOUND 1 TEST) — ядро AudioPinkNoiseOn (20а);

— тест SCART DVD — ядро VideoScartSwDvd (54а);

— тест SCART LOOP — ядро VideoScartSwPass (54b);

— 2-й звуковой тест (SOUND 2 TEST) — ядро AudioSineOn (21а).

Рассмотрим каждый из этих тестов подробнее.

Видеотест (PICTURE TEST) позволяет проверить видеотракт проигрывателя. При активации этого теста на индикаторе появится сообщение «АРР PIC—1».

При этом на видеовыходы проигрывателя поступает сформированный им сигнал цветных полос, и на подключенном к ним телевизоре должно появиться соответствующая испытательная картинка. Если отображается испытательная картинка, то следует нажать кнопку <EJECT>, а если нет (отсутствует или искажена), то — кнопку <STOP>. Для перехода к выполнению следующего теста необходимо нажать кнопку <PLAY/PAUSE>.

1-й звуковой тест (SOUND 1 TEST) и тест SCART DVD обеспечивают формирование сигнала «розового» шума, который должен быть слышен в подключенных к проигрывателю громкоговорителях, а на дисплее в течение некоторого небольшого промежутка времени будет индицироваться сообщение «АРР SND — 1».

После запуска 1-го звукового теста (SOUND 1 TEST) будут активны сигналы на выходах разъема SCART, если он установлен в аппарате. При этом на дисплее появится сообщение «SCART DVD», на экране телевизора будут цветные полосы (от SCART), а в громкоговорителях будет слышен «розовый» шум. Если шум не слышен,

то следует нажать кнопку <STOP>, а если тест прошел нормально — кнопку <EJECT>. Для перехода к выполнению следующего теста нажимают кнопку <PLAY/PAUSE>. Если в аппарате нет разъема SCART, то следует сразу, не нажимая кнопки <STOP> и <EJECT>, нажать <PLAY/PAUSE>, что будет воспринято программным обеспечением как нормальное прохождение теста.

Тест SCART LOOP позволяет проверить прохождение сигналов с разъемов SCART. Подтверждением активации этого теста является сообщение «SCART LOOP» на экране индикатора. Нажатие кнопки <PLAY/PAUSE> включает внешний источник от SCART, а очередное нажатие кнопки <EJECT> переключает на SCART внутренний испытательный сигнал. Из теста можно выйти, если нажать и удерживать кнопку <PLAY/PAUSE> более одной секунды.

2-й звуковой тест (SOUND 2 TEST) формирует синусоидальный сигнал на аудиовыходах, который хорошо слышен в громкоговорителях, а на дисплее будет индицироваться сообщение: «АРР SND — 2». Генерацию этого сигнала можно прекратить кнопкой <STOP>. Если после этого нажать кнопку <EJECT>, то это подтверждает положительный результат проверки. Если синусоидальный сигнал не слышен или искажен, то следует повторно нажать кнопку <STOP>. Для перехода к выполнению следующего теста нажать кнопку <PLAY/PAUSE>. Если, не нажимая кнопки <STOP> и <EJECT>, нажать <PLAY/PAUSE>, то это будет воспринято ПО как нормальное прохождение теста.

Тест сервоузла главной платы (моноплаты) и узла привода

Тест сервоузла моноплаты и узла привода будем называть далее сокращенно «тестом узла привода». Этот тест можно разделить на семь тестов, каждый из которых выполняется соответствующим ядром сценария Player Script, причем тест управления лотком выполняется дважды (см. также рис. 5.20):

— номер версии привода (VERSION NUMBER) — ядро BeVer (37);

— тест управления лотком (TRAY TEST) — ядро BeTrayOut/ln (43ab);

— тест движения салазок лазерной головки (SLEDGE TEST) — ядро BeSledgeOut/ln (41 ab);

— тест шпинделя диска (DISC MOTOR TEST) — ядро BeDiscMotorOn (39а);

— тест привода фокусировки (FOCUS TEST) — ядро BeFocusOn (38а);

— тест радиальной коррекции (RADIAL TEST) — ядро BeRadialOn (40а);

— тест быстрой установки головки на дорожки (JUMP TEST) — ядро BeGroovesln/Mid/Out (42abc);

— тест управления лотком (TRAY TEST) — ядро BeTrayOut/ln (43ab).

Номер версии привода (VERSION NUMBER) выводится на индикаторе проигрывателя сразу после перехода к исполнению теста узла привода. Это сообщение может быть следующим: «BE -05 01 14».

Для старта основного тела теста узла привода, следует нажать кнопку <PLAY/PAUSE>.

Тест управления лотком (TRAY TEST) также не является тестом в привычном понимании и не влияет на общий результат тестирования. При активации этого теста на индикатор выводится сообщение: «DO — BE TRAY». Тест управления лотком (TRAY TEST) необходим только для того, чтобы загрузить тестовый диск для проведения визуальных и слуховых тестов, по окончании которых тест управления лотком активируется опять для выгрузки диска.

Кнопки <EJECT> и <STOP> позволяют менять положение лотка. Для перехода к следующему тесту после загрузки диска необходимо нажать кнопку <PLAY/PAUSE>. Кроме того, ПО закроет лоток автоматически, если он был открыт.

Тест движения салазок лазерной головки (SLEDGE TEST) относится к разряду визуальных тестов, результат которых не фиксируется. При активации этого теста на индикатор выводится сообщение: «DO — BE SLED». Кнопки <EJECT> и <STOP> позволяют многократно менять позиционирование лазерной головки, наблюдая за исполнением команд визуально, что требует частичной разборки аппарата. Для перехода к следующему тесту необходимо нажать кнопку <PLAY/PAUSE>.

Тест шпинделя диска (DISC MOTOR TEST) — это также визуальный тест, активация которого обеспечивает раскрутку двигателя шпинделя ди-ска.. Он сопровождается сообщением «АРР BE DISC» на индикаторе. Нажатием кнопки <EJECT> подтверждается вращение шпинделя диска, а нажатием кнопки <STOP> — двигатель не запустился. Для перехода к выполнению следующего теста необходимо нажать кнопку <PLAY/PAUSE>. Если сразу нажать кнопку <PLAY/PAUSE>, не нажимая до того <STOP> и <EJECT>, то это будет воспринято ПО как нормальное прохождение теста.

Тест привода фокусировки (FOCUS TEST) также является визуальным. При его запуске происходит небольшое смещение лазерной головки по оси и на индикаторе появляется сооб—

щение «АРР BEFOCUS». Дальше также как в предыдущем случае.

Нажатием кнопки <EJECT> подтверждается успешная фокусировка, а нажатием кнопки <STOP> — проблемы с ней. Для перехода к выполнению следующего теста необходимо нажать кнопку <PLAY/PAUSE>. При этом происходит отключение регулировки фокусировки. Если сразу нажать кнопку <PLAY/PAUSE>, не нажимая до того <STOP> и <EJECT>, то это будет воспринято ПО как нормальное прохождение теста.

Гест радиальной коррекции (RADIAL TEST) как визуальный, так и слуховой тест, т. е. о его прохождении судят как по качеству изображения, так и по качеству звука считываемых с диска. При активации этого теста на индикатор выводится сообщение «АРР BERADIA». Нажатием кнопки <EJECT> мы подтверждаем работу радиального смещения головки, а нажатием кнопки <STOP> сообщаем ПО о том, что его нет. Для перехода к выполнению следующего теста необходимо нажать кнопку <PLAY/PAUSE>. Если сразу нажать кнопку <PLAY/PAUSE>, не нажимая до того <STOP> и <EJECT>, то это будет воспринято ПО как нормальное прохождение теста.

Гест быстрой установки головки на дорожки (JUMP TEST) является слуховым тестом. Он сопровождается сообщением «DO BE GROO». Этот тест не влияет на общий результат тестирования. Кнопки <EJECT> и <STOP> позволяют циклически переключать ядра BeGroovesIn, BeG-roovesMid и BeGroovesOut, которые устанавливают лазерную головку на различные дорожки диска. Нажав кнопку <PLAY/PAUSE> после остановки шпинделя, можно перейти к тесту управления лотком (TRAY TEST) для того, что бы достать диск. После чего необходимо нажать кнопку <PLAY/PAUSE>. Лоток закроется и запустится команда считывания регистра ошибок (ядро Log-ReadErr(31)).

Считывание регистра (Error Log) и бит ошибок

При активации ядра LogReadErr и чтении кода из регистра ошибок на индикатор проигрывателя выводится сообщение, в левой части которого расположен идентификатор операции чтения регистра ошибок («EL»), а в правой код ошибки. Коды зарегистрированных ошибок можно прокручивать циклически кнопками <EJECT> (вверх) и

Таблица 5.13. Коды и биты ошибок

| Краткое описание ошибки | Код ошибки | Бит ошибки |

| Ошибки привода и сервочасти главной платы | ||

| Команда недоступна для данного состояния привода или неверная команда | 150101 | 8 |

| Для данной команды не действительы заданные параметры | 150102 | 7 |

| Лазерная головка не может бить установлена в начальную позицию (home position) | 150103 | 6 |

| Отказ системы фокусировки | 150104 | 5 |

| Двигатель шпинделя диска не смог достичь необходимой скорости в отведенное для этого время | 150105 | 4 |

| I Лазерная головка не попадает точно на дорожку (ошибка трекинга — Radial) | 150106 | 3 |

| 1 Отсутствие блокировки ФАПЧ при доступе или наличие ее в состоянии слежения | 150107 | 2 |

| Не читается субкод или информация о секторе | 150108 | 1 |

| Запрошенный субкод не найден | 150109 | 16 |

| Лоток не закрылся или не открылся полностью | 15010А | 15 |

| Содержание (ТОС) не было прочитано в отведенное для этого время | 15010В | 14 |

| Запрошенный поиск на диске не мог быть выполнен | 15010С | 13 |

| Запрошенной вводной дорожки нет на диске | 15010D | 12 |

| Запрошенная область вырезана, нет пакетов | 15010Е | 11 |

|

|

1501F0 | Ю |

| 1501F1 | 9 | |

| Ошибка связи по цифровой шине S2B | 1501F3 | 24 |

|

|

1501F4 | 23 |

| 1501F5 | 22 | |

| Ошибки цифровой части главной платы | ||

| Ошибка связи с процессором STi5508 (STi5580) | 90000 | 32 |

| 90001 | 31 | |

| Ошибки платы дисплея | ||

| Ошибка связи с процессором дисплея | 190000 | 40 |

Рис. 5.25. Сообщение на индикаторе при циклическом (закольцованном) тесте

<STOP> (вниз). Возможные коды ошибок представлены в табл. 5.13. Если при считывании регистра ошибок все значения равны 0, это значит, что ошибок нет.

Нажатие кнопки <EJECT> приводит к считыванию битов ошибок. При этом на индикаторе появится сообщение, в левой части которого расположен идентификатор операции чтения битов ошибок («ЕВ»), а в правой бит ошибки представленный десятичным числом (см. биты ошибок в табл. 5.13). Зарегистрированные биты ошибок можно прокручивать кнопками <EJECT> (вверх) и <STOP> (вниз).

Циклический тест (LOOP TEST)

Очередное нажатие кнопки <EJECT> активирует циклический (закольцованный) тест (LOOP TEST). Сценарий этого теста сдержит, практически, те же ядра-команды, что и Dealer Script, но при прохождении этого теста на индикаторе будет демонстрироваться результат проверок в виде сообщения (см рис. 5.25 и табл. 5.14). Так, как тест закольцованный, то он будет продолжаться непрерывно (цифры сообщения все время будут меняться), до тех пока включено напряжение питания.

Трехзначное двоичное число в левой части на рис. 5.25 указывает на результат циклического (закольцованного) теста, т е. на состояние каждого из проверяемых узлов.

Таблица 5.14

Состояние основных узлов по результатам циклического теста

|

Индицируемое значение

(см рис 23 слева) |

Состояние каждого из узлов | ||

|

Сервочасть

главной платы и привод |

Цифровая часть главной платы | Плата дисплея | |

| 000 | норма | норма | норма |

| 001 | норма | норма | отказ I |

| 010 | норма | отказ | норма |

| 011 | норма | отказ | отказ |

| 100 | отказ | норма | норма |

| 101 | отказ | норма | отказ |

| 110 | отказ | отказ | норма |

| 111 | отказ | отказ | отказ |

Таблица 5.15

Коды ошибок выявляемых при циклическом (закольцованном) тесте

| Коды ошибок | Номера ядер |

Описание ошибок

i |

| 0601 | 6 | Вычисленная контрольная сумма FLASH-памяти неверна |

| 1101 | 11 | Шина 12С занята перед запуском |

| 1102 |

|

Нет доступа к энергонезависимой памяти NVRAM |

| 1103 |

|

Нет сигнала подтверждения от ' энергонезависимой памяти NVRAM |

| 1104 |

|

Нет ответа NVRAM |

| 1201 | 12 | Шина 12С занята |

| 1202 |

|

Шина 12С не функционирует 1 |

| 1203 |

|

Ведомый процессор не отвечает |

| 1204 |

|

Ответ ведомого неверен |

| 1301 | 13 |

Ошибка четности

последовательного интерфейса S2B при передаче данных от сервопроцессора |

| 1302 |

|

! Ошибка четности

последовательного интерфейса S2B при передаче данных на сервопроцессор |

| 1303 |

|

Нет связи между шиной S2B и сервопроцессором |

| 1304 |

|

Сбой временной блокировки связи |

| 1601 | 16 | Неисправна SDRAM |

| 5201 | 52 | Шина I2C занята |

| 5202 |

|

Ошибка передачи команды включения цветности по шине 12С |

| 5203 |

|

Микросхема, включающая цвет не отвечает |

| 5204 |

|

Микросхема, включающая цвет отвечает неверно |

| 5401 | 54 | Шина 12С занята |

| 5402 |

|

Ошибка передачи по шине 12С команды переключения SCART |

| 5403 |

|

Схема переключения SCART не 1 отвечает |

| 5403 |

|

Схема переключения SCART отвечает неверно |

remontdvd.narod.ru Информация получена из открытых источников